集成电路工艺公式&其他一些杂七杂八

- 氧化: : ( 是单位面积的分子密度)(用 原子数相等作为条件)

- 离子注入:mask的厚度计算(经验公式): ( 是厚度, 是纵向射程, 是纵向标准偏差)( )

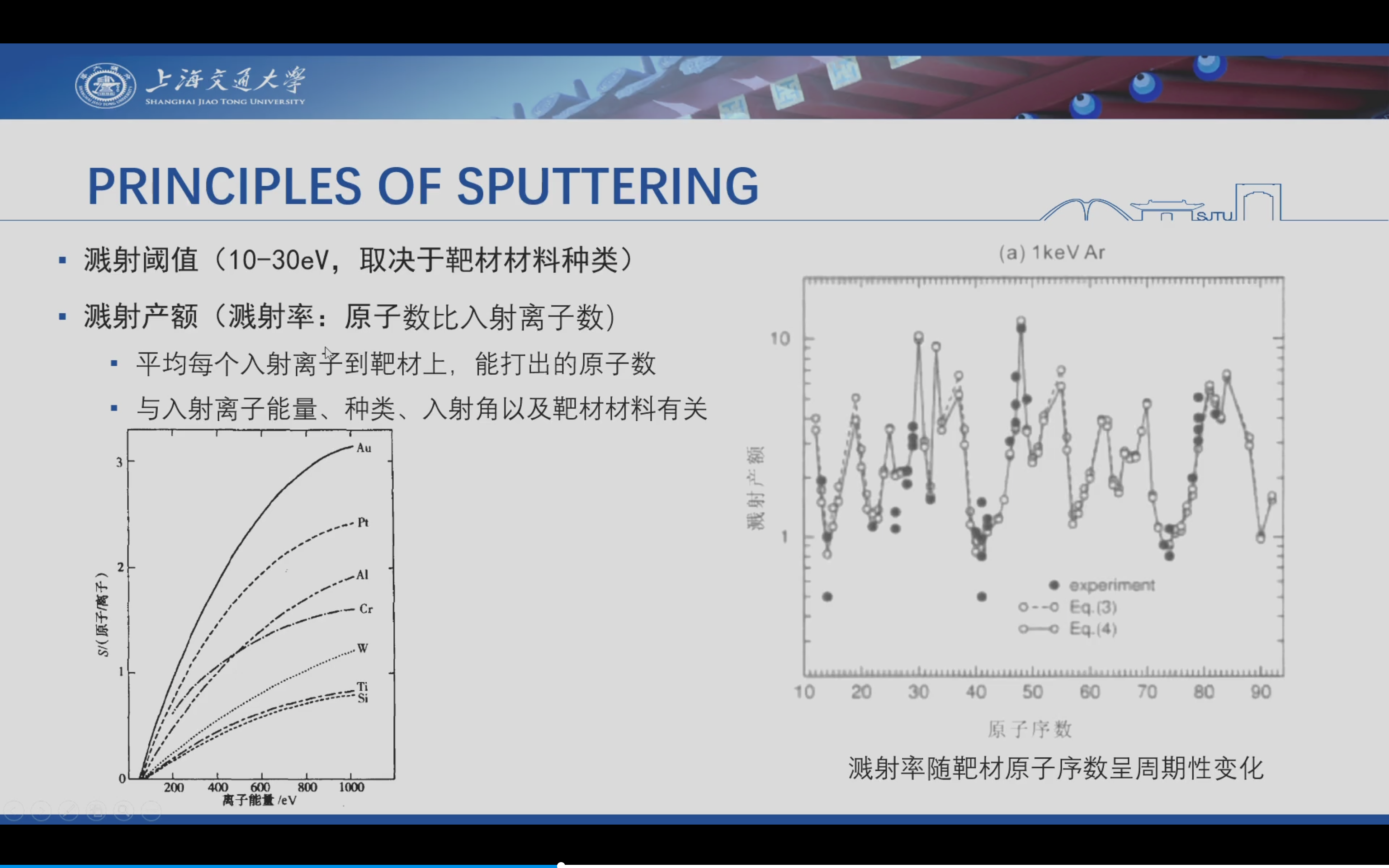

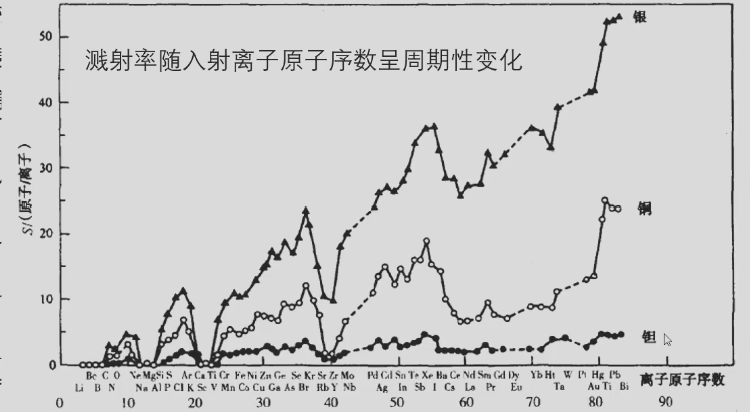

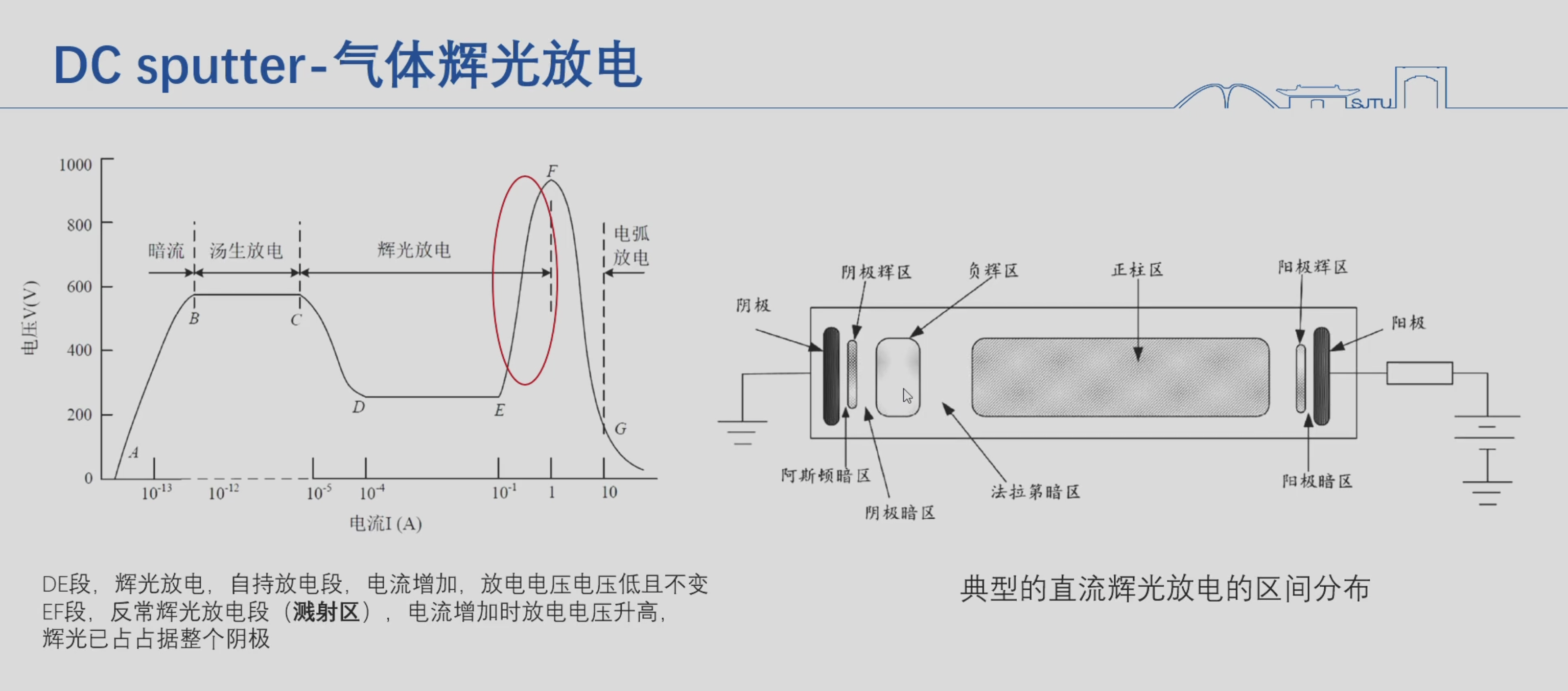

- PVD补充

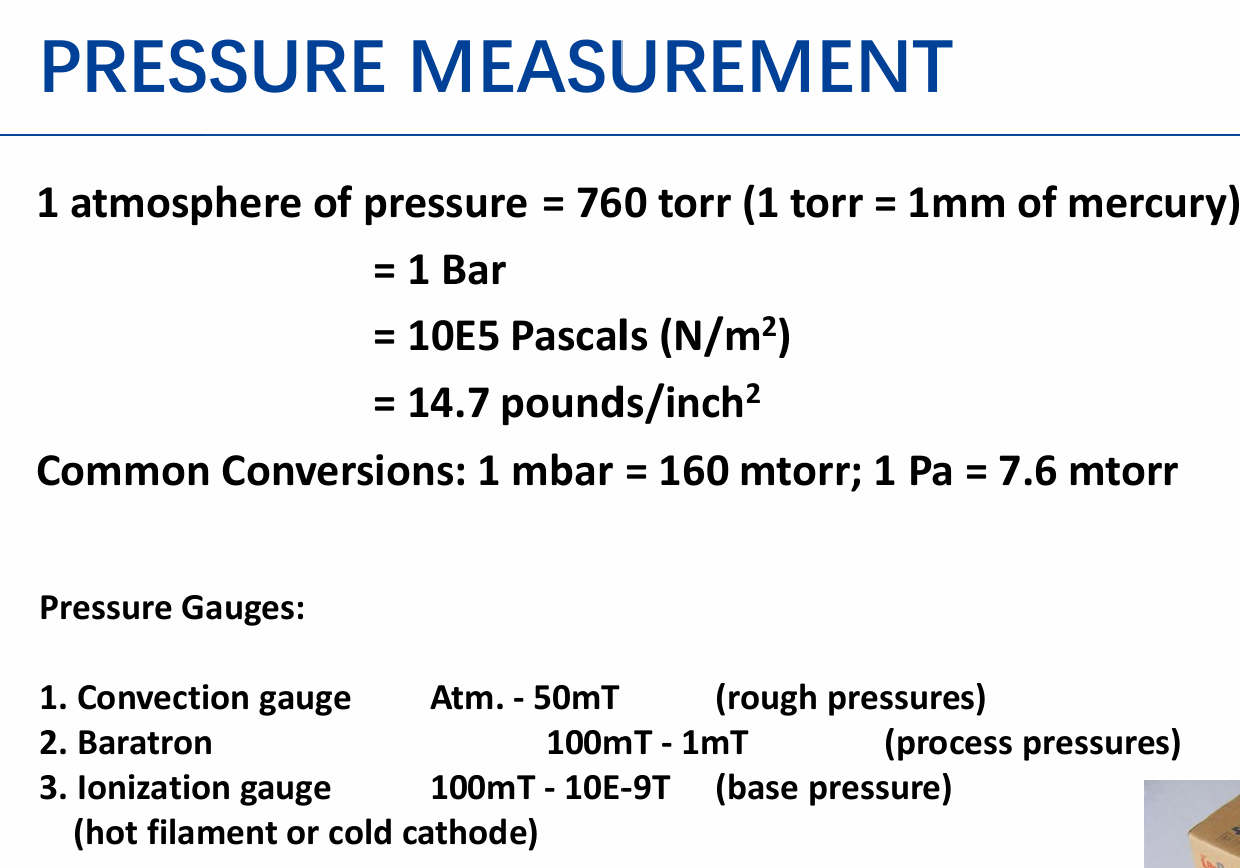

- Pressure

- PVD:dep rate 沉积速率 space 靶和衬底的距离

- AR是深宽比,比如是2,宽度50,深度最多100

- 光刻:

- 在接触光刻与接近光刻的情况下,最小分辨尺寸

- 投影光刻

- 最小分辨尺寸 其中 是与镜头有关的参数。

- DOF(焦深): ,越大越好

- 浸入光刻: ,

- 光刻胶厚度公式:PPT136页

- 瑞利判据:

- 刻蚀程度

额外知识:

High-k

在集成电路工艺中,"High-K介质"指的是具有高介电常数(k值大于3.9)的电介质材料,这些材料被用来替代传统的二氧化硅(SiO2)作为栅介质。这种材料的主要优势在于其较高的介电常数,使得在保持相同栅电容(COX)的情况下,可以使用更厚的介质层,从而减少栅极泄漏电流,提高晶体管的性能和可靠性。

随着集成电路特征尺寸的不断缩小,传统的SiO2栅介质已经无法满足更高性能晶体管的需求。当栅介质厚度降低到一定程度时,会因为隧穿效应导致漏电流急剧增加,影响晶体管的性能。High-K介质材料,如氧化铪(HfO2),其介电常数远高于SiO2(SiO2的k值约为3.9,而HfO2的k值约为20),这使得在相同的等效氧化层厚度(EOT)条件下,可以使用更厚的High-K介质层,从而有效降低栅极漏电流。

High-K介质的应用也带来了一些挑战,比如与现有硅栅极的兼容性问题,以及可能引起的载流子迁移率降低等。为了解决这些问题,通常会采用金属栅极(Metal Gate)技术与High-K介质配合使用,这种技术组合被称为HKMG(High-K Metal Gate)技术。通过这种技术,可以在保持晶体管性能的同时,进一步减小晶体管尺寸,提高集成电路的集成度和性能。

光�刻制程

光刻的主要步骤:清洁硅片-涂覆光刻胶-软烘-对准和曝光-显影-硬烘-刻蚀-去胶

LOCOS

LOCOS(Local Oxidation of Silicon,硅局部氧化隔离)技术是一种在CMOS硅工艺中常用的器件隔离技术。这项技术通过在硅衬底表面局部氧化生成厚的二氧化硅层来隔离器件。具体来说,LOCOS工艺利用氮化硅(Si3N4)作为掩膜层,实现硅的选择性氧化。在这种工艺中,除了形成有源晶体管的区域以外,在其他所有重掺杂硅区上均生长一层厚的氧化层,这层氧化层被称为隔离或场氧化层。

LOCOS工艺的基本步骤包括:

- 生长前置氧化层(PAD Oxide),作为缓冲层减少应力。

- 生长Si3N4层,作为场区氧化的阻挡层。

- 有源区(Active Area)光刻和刻蚀处理。

- 场区氧化,形成硅局部场氧化物隔离器件。

- 刻蚀去除Si3N4层。

然而,LOCOS技术存在一些限制,最主要的问题是“鸟嘴效应”(Bird's Beak),即在氧化过程中,氮化硅掩膜层边缘的硅区域也会被氧化,形成类似鸟嘴的结构,这会导致有源区的有效面积减少,限制了隔离区宽度的进一步缩小。此外,LOCOS工艺还可能产生Kooi效应(白带效应),即高温下氨气与硅衬底反应生成的Si3N4。

由于这些限制,LOCOS技术在深亚微米工艺中逐渐被STI(Shallow Trench Isolation,浅沟槽隔离)技术所取代,STI技术能更有效地隔离器件并减少占用的面积。

Latch-up 效应

Latch-up效应,也称为闩锁效应,是CMOS集成电路中的一种潜在破坏性现象。它指的是在CMOS芯片中,由于寄生的NPN和PNP三极管相互导通,导致在电源VDD和地VSS之间产生低阻抗通路,从而引发大电流的一种机制。长时间的大电流可能会对芯片造成永久性的损坏。

具体来说,Latch-up效应通常由以下几个条件触发:

- 寄生三极管的导通:在CMOS集成电路中,由于工艺原因,会形成寄生的PNPN结构,这些结构在某些条件下可以形成类似硅控整流器(SCR)的器件,具有正反馈效应。

- 触发因素:Latch-up可能由电流注入、过电压、电压瞬变、静电放电(ESD)或者高功率微波脉冲等外部因素触发。

- 正反馈形成:一旦寄生的NPN和PNP三极管导通,就会形成正反馈,使得VDD和VSS之间的电流不断增大,导致电路功能失效或器件损坏。

Latch-up效应的后果可能包括:

- 功能失效:电路可能暂时失效,移除触发因素后恢复正常。

- 系统关闭:可能需要关闭系统以清除低阻抗路径。

- 器件损坏:在严重情况下,可能需要更换损坏的部件。

为了抑制Latch-up效应,可以采取以下措施:

- 版图设计优化:通过减少衬底和N阱的寄生电阻,避免寄生的三极管处于正偏状态。

- 增加阱和衬底接触:提供大量的阱和衬底接触以避免Latch-up效应。

- 使用保护环(Guard ring):减少电阻,防止潜在的电流注入。

- 隔离沟槽(Isolation trench):避免非期望的电流泄漏或电流传导路径。

随着��工艺的改进和设计的优化,Latch-up效应的风险已经大大降低,但在某些应用中仍然是一个需要关注的问题。

Anti-punchthrough implantation(PTI)

Anti-punchthrough implantation(PTI)是一种在CMOS技术中用来抑制短沟道效应(Short-Channel Effects, SCEs)的技术,特别是用来防止沟道长度调制效应(punchthrough)。在CMOS晶体管中,随着沟道长度的减小,晶体管的控制能力会降低,导致漏电流增加和阈值电压降低,这种现象称为短沟道效应。PTI通过在晶体管的源/漏区域下方引入一个高掺杂区域,来增加沟道的电阻,从而减少漏电流和提高阈值电压,增强晶体管的性能和可靠性。

具体来说,PTI是在晶体管的整个沟道长度下方,靠近栅氧层(gate oxide)的地方,植入一个高掺杂的区域。在n沟道MOSFET(nMOSFET)中,PTI区域是高掺杂的p型区域,而在p沟道MOSFET(pMOSFET)中,则是高掺杂的n型区域。这种植入可以减少由于沟道长度缩短导致的晶体管性能退化,如阈值电压的降低和漏电流的增加。

此外,PTI还与源/漏区域的晕区(halos)植入相结合,晕区是位于源/漏扩展区域附近的高掺杂体区域,它们共同作用以进一步抑制短沟道效应,并提高晶体管的静电放电(ESD)保护能力。通过这些技术的应用,可以制造出更小、更快且更可靠的CMOS器件。

Halo implantation

Halo implantation(晕环注入)是一种在CMOS(互补金属氧化物半导体)技术中用于提高器件性能和抑制短沟道效应(Short-Channel Effects, SCEs)的离子注入工艺。这种技术通过在MOSFET的源/漏区域下方引入高掺杂区域,形成所谓的“晕环”或“halo”,来改善器件的特性。

具体来说,Halo implantation的目的包括:

- 抑制短沟道效应:随着MOSFET特征尺寸的缩小,短沟道效应成为限制器件性能的关键因素之一。Halo结构能够有效抑制这些效应,改善小尺寸器件的性能。

- 提高温度稳定性和工艺容差:合理的Halo区掺杂分布可以改善器件在不同温度下的性能,以及提高对工艺波动的容忍度。

- 优化掺杂分布:通过调整Halo注入的倾角和能量,可以优化器件的掺杂分布,从而改善常温和高低温下的特性。

Halo implantation过程中,不仅需要严格控制掺杂剂量,还需要精确控制掺杂粒子的植入位置。现代离子注入机通过控制离子束的入射角度来管理这些挑战,以适应亚90纳米器件集成和性能需求。随着器件几何尺寸的缩小,对Halo植入角度的敏感性也在增加,因此必须精确控制Halo植入角度,以确保不同离子注入机之间的无缝工艺和器件匹配。

总的来说,Halo implantation是一种关键的工艺步骤,它通过在MOSFET的源/漏区域下方形成高掺杂区域,来提高器件的性能和可靠性,特别是在深亚微米技术节点中。

LDD

Light Drain Doping(LDD),即轻掺杂漏,是一种在CMOS技术中用于提高器件性能和可靠性的工艺技术。其主要目的是减弱漏区电场,改进热电子退化效应,特别是在亚微米和深��亚微米尺寸的MOSFET中,这种结构尤为重要。

LDD技术通过在沟道中靠近漏极的附近设置一个低掺杂的漏区,让这个低掺杂的漏区也承受部分电压,从而降低漏极附近的电场强度。这种结构可以有效防止热载流子注入效应(Hot Carrier Injection, HCI),因为HCI会导致载流子能量超过Si-SiO2的势垒高度,使得热载流子能直接注入或通过隧道效应进入SiO2,对栅氧造成破坏,进而导致器件性能退化或损伤。

在LDD工艺流程中,通常会在栅极的边界下方与源漏之间形成低掺杂的扩展区,这个扩展区在源漏与沟道之间形成杂质浓度梯度,减小漏极附近的峰值电场,达到改善HCI效应和器件可靠性的目的。对于NMOS,LDD通常使用磷(P)和砷(As)作为掺杂剂,而对于PMOS,则使用硼(B)和二氟化硼(BF2)。

LDD结构已经成为大规模集成电路中MOSFET的基本结构,它通过优化掺杂分布来提高器件的性能和可靠性。